Paper Name: Reconfigurable FPGA based Multifunction Image

Processor

Conference Name: International Conference on Communication

Technology ICCT 2015

Authors: Shivank Dhote(Vidyalankar Institute of Technology),

Zalak Dave (Eduvance), Pranav Charjan (Vidyalankar Institute of

Technology), Dr. Jonathan Joshi (Eduvance) and Ganesh Gore

(Eduvance)

Abstract: Image processing (I.P.) systems, involving multiple

processing functionalities, use standard software tools to

manipulate pixel values. The load on the system is high when these

software tools are used for real time I.P. applications as the

system they are running on are systems that are not specific to a

particular application. This would require either high end

hardware systems or an application specific hardware. Field

Programmable Gate Arrays (FPGA) provide a cost effective

customizable solution. The Command Controlled Image Processor

proposed in this paper provides a specific hardware based solution

which is designed only for certain specific image processing

tasks. This paper deals with the design and implementation of a

multifunction processor with different modules using a FPGA. The

design has been prototyped on a Xilinx Spartan 3E FPGA. The

expected and achieved outputs have been given with comparison to

standard MATLAB outputs. The hardware occupancies and delays have

also been reported for different FPGA devices.

Paper Name: Optimizing power consumption in Iot based wireless

sensor network using Bluetooth Low Energy

Conference Name: ICGCIOT, International conference on Green

computing and Internet of Things

Authors: Karan Nair (Eduvance), Janhavi Kulkarni (Eduvance),

Mansi Warde (Eduvance), Zalak Dave (Eduvance), Vedashree

Rawalgaonkar (Eduvance), Ganesh Gore (Eduvance) and Dr. Jonathan

Joshi (Eduvance)

Abstract: The use of chaos for image encryption over traditional

text based encryption methods has gained momentum due to its

superior performance. In this paper, a fast encryption method is

presented which utilizes a substitution-permutation network using

two chaotic maps. Logistic maps are used to create substitution

box while key dependent rectangular chaotic maps is used for

permutation of pixels. The algorithm is applicable to images of

any dimension. It shows improved performance and a good level of

security.

Paper Name: A Low Cost Power Oscilloscope for Educational

Platform using PSoC.

Conference Name: International Conference on Advances in

Communication and Computing Technologies 2014

Authors: Ameya Wagh (Fr Conceicao Rodrigues Institute of

Technology), Zalak Dave (Eduvance), Gaurav Singh (Padmabhushan

Vasantdada Patil Pratishthan's College of Engineering), Varun

Dange (Padmabhushan Vasantdada Patil Pratishthan's College of

Engineering), Abhay Tambe (Reanu Microelectronics Private

Limited) and Sachin Gengaje (Walchand Institute of Technology).

Abstract: This paper discusses the design and implementation of a

portable oscilloscope using a programmable system on chip (PSoC).

The main aim of this paper is to highlight the use and need of a

low cost system for student applications. The system was

implemented using a PSoC 4 device and a Nokia 5110 LCD screen.

Performance metrics were measured and compared to show tradeoffs

between cost and performance.

Paper Name: Single chip DDS using PSOC with on-Chip Signal

Conditioning and Capacitive Touch Sensor

Conference Name: Itechcon 2014 by Vivekanand Education Society's

Institute of Technology.

Authors: Sriram Viswanathan (Vivekanand Education Society's

Institute of Technology), Pratik Shirke (Vivekanand Education

Society's Institute of Technology), Gopalkrishnan Narayanan

(Vivekanand Education Society's Institute of Technology) and

Ganesh Gore (Eduvance).

Abstract: This paper discusses the design and implementation of a

single chip direct digital synthesizer (DDS) using a programmable

system on chip (PSoC). The design of the DDS takes into account

signal conditioning for high loads presented by probes of scopes

and circuits. We have implemented the variation of frequency using

a capacitive touch control and the ability to generate custom

waveforms thus making this DDS reconfigurable, along with

discussing features of small size and low cost.

Paper Name: Image Encryption Using Logistic And Rectangular

Chaotic Maps

Conference Name: IEEE Indicon, 2015

Authors: Karan Nair (K J Somaiya College Of Engineering),

Janhavi Kulkarni (K J Somaiya College Of Engineering), Vicky

Chedda (K J Somaiya College Of Engineering), Dr. Jonathan Joshi

(Eduvance),Ganesh Gore (Eduvance).

Abstract: The use of chaos for image encryption over traditional

text-based encryption methods has gained momentum due to its

superior performance. In this paper, a fast encryption method is

presented which utilizes a substitution-permutation network using

two chaotic maps. Logistic maps are used to create substitution

box while key dependent rectangular chaotic maps is used for

permutation of pixels. The algorithm is applicable to images of

any dimension. It shows improved performance and a good level of

security

Paper Name: Implementing Semi-Blind Image Steganography With

Improved Concealment

Conference Name: ICCT 2015 - International Conference On

Communication Technology

Authors: Karan Nair (Eduvance),Karan Asher (K J Somaiya College

of Engineering), Dr. Jonathan Joshi (Eduvance).

Abstract: There have been a number of proposed methods to conceal

information using steganographic techniques. Images are the

favored carrier due to the large capacity for concealed

information and relative ease to work with. A number of methods

exist to conceal text as well as image data within images. This

paper proposes an information embedding scheme with improved

concealment of secret images within larger images using a

fractional embedding scheme. It explores the natural redundancy of

image data, as well as limitations of human perception and

statistical attacks to provide better subjective and objective

concealment.

Paper Name: Spatial Domain Video Encryption Using Chaotic

Maps

Conference Name: ICCT 2015 - International Conference On

Communication Technology

Authors: Karan Nair (Eduvance), Janhavi Kulkarni (Eduvance),

Karan Asher (K J Somaiya College of College of Engineering), Dr.

Jonathan Joshi (Eduvance).

Abstract: Digital video is one of the most popular multimedia data

exchanged over the internet. Previous cryptography studies have

focused on text data. The encryption algorithms developed for text

data may not be suitable to multimedia applications because of

large sizes of video. An algorithm is proposed in which a video

file is encrypted by considering each frame a color image. Each

video is broken down into its constituent frames. Chaotic mapping

algorithms are applied on all the frames and in the temporal

domain of the video as well. The algorithm was run on different

videos, and results were obtained show improved performance time

and good security. Initial comparison against existing methods

also shows that encryption time required is less, while recovered

plaintext also has fewer distortions.

Paper Name: Implementing A Cloud Based Xilinx ISE FPGA Design

Platform For Integrated Remote Labs

Conference Name: ICACI 2015 - International Conference On

Advances In Computing, Communications And Informatics

Authors: Jinal Kumar Doshi (Sardar Patel Institute of

Technology),Pratiksha Patil (Sardar Patel Institute of

Technology), Zalak Dave (Eduvance),Ganesh Gore (Eduvance),Dr.

Jonathan Joshi (Eduvance), Reena Sonuskare, Surendra Rathod

(Sardar Patel Institute of Technology).

Abstract: This paper describes the implementation of a cloud based

Xilinx ISE platform that can be used by the users remotely. The

Remote Xilinx environment is used to provide remote access to the

Xilinx Integrated Software Environment (ISE). The main aim of the

research presented is to highlight how users can access FPGA

design resources from anywhere in combination with a potential

remote FPGA lab. The architecture of the cloud based platform is

described with a load analysis for the server. The cloud based

approach has been proposed and a comparative analysis is discussed

based on the results obtained. The remote environment is developed

on the Ubuntu (open source) operating system by using Python and

Hypertext Preprocessor (PHP) scripting languages. The open source

Apache server is used for running Xilinx environment on a server

and open source analysis tools are used to perform server load

analysis for running Xilinx environment on the server system.

Paper Name: Network On Chip Based Multi-Function Image

Processing System Using FPGA

Conference Name: ICACI 2015 - International Conference On

Advances In Computing, Communications And Informatics.

Authors: Zalak Dave(Eduvance), Shivank Dhote(Vidyalankar

Institute of Technology), Dr.Jonathan Joshi (Eduvance), Ganesh

Gore (Eduvance), Abhay Tambe (Reanu Microelectronics), Dr.Sachin

Gengaje (Walchand Institute of Technology).

Abstract: Multifunction parallel image processing systems use

standard buses to do inter core communication. Faster and scalable

approaches are needed to improve the throughput of the system, but

for data heavy applications like Image Processing (IP) algorithms

there is a need for constant data transfer between different

functional blocks on chip. The solution would either be hardwired

buses or controlled communication. Networks-On-Chip (NoC) present

a systematic solution, and can succeed a hardwired bus solution in

a scalable form. This paper presents a multifunction image

processing system prototyped on a single reconfigurable platform.

The different IP cores have been implemented keeping in mind

on-the-fly processing times and frame rates. The different modules

are interconnected using a Torus architecture NoC with an

information heavy packet structure and capable of addressing

multiple nodes simultaneously. The implementation was done using a

low cost Spartan 6 FPGA. Frame rates for standard sizes and chip

utilization has been reported.

Paper Name: Spatial Domain Video Encryptionand Authentication

using Chaotic Maps and Secure Whirlpool Hash

Conference Name: ICCT 2015 : International Conference on

Communication Technology

Authors: Karan Nair, Janhavi Kulkarni, Karan Asher, Vicky

Chedda, Jonathan Joshi

Abstract: Digital video is one of the most popular multimedia data

exchanged over the internet. Previous cryptography studies have

focused on text data. The encryption algorithms developed for text

data may not be suitable to multimedia applications because of

large sizes of video. We present an algorithm in which a video

file is encrypted by considering each frame as acolour image. Each

video frame is broken down into RGB planes. Chaotic mapping

algorithms are applied on all the planes of each frame, the

temporal and horizontal domain of the video. For end-to-end

authentication, semantically secure whirlpool hash has been used.

Data integrity is verified using XOR hash which can detect

tampering of data at any intermediate node. The algorithm was run

on different videos, and satisfying results were obtained.

Paper Name: Secure Semi-Blind Steganography using Chaotic

Transforms

Conference Name: 2016 3rd International Conference on "Computing

for Sustainable Global Development" , New Delhi (India), IEEE

Xplore

Authors: Janhavi Kulkarni, Karan Nair, Mansi Warde, Vedashree

Rawalgaonkar, Jonathan Joshi

Abstract: Secure digital data is a current need of the hour.

Increasing computational power makes brute force attacks on

cryptographic systems a feasible attack, requiring higher key

length to protect data. On the other hand, concealing data using

steganography always leaves a trace. Hence, embedding of data

directly in steganography is not secure as the system is only

secure until the concealment is not discovered. A hybrid solution

to the problem is proposed in this paper where cryptographic

functions are incorporated in the embedding process of

steganography

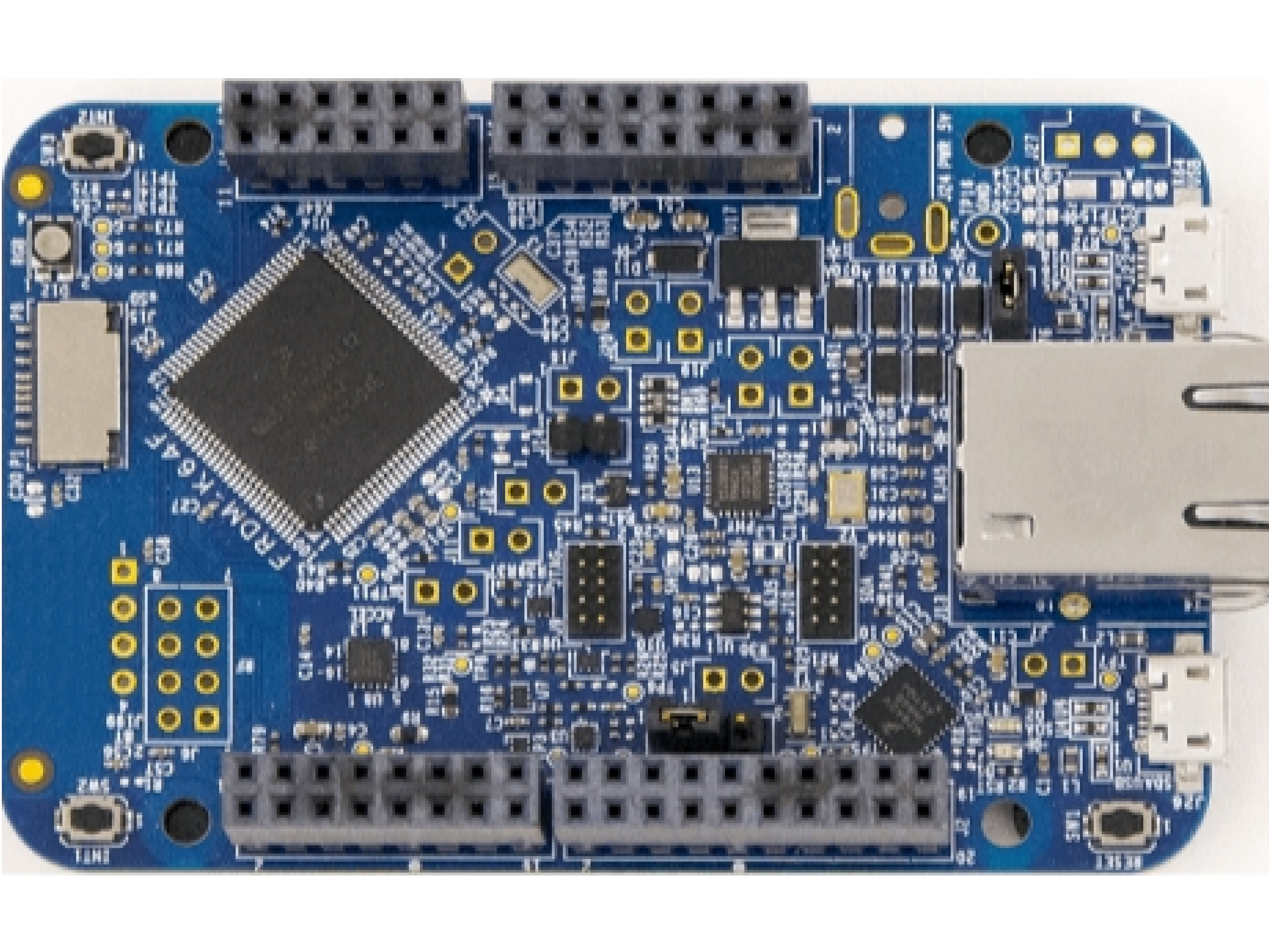

Paper Name: Low Cost SoC-FPGA interface for IoT based Image

processing

Conference Name: 5th International Conference on Advances in

Computing, Communications and Informatics 2016 (ICACCI '16),

Jaipur.

Authors: Shivank Dhote, Pranav Charjan, Aditya Phansekar, Aniket

Hegde, Sangeeta Joshi

Abstract:Multifunction image processing systems are typically

deployed at the application site, but with the advent of Internet

of Things(IoT) the design of such systems that are accessible

remotely by applications over the internet is the need of the

hour. These systems, being designed for data heavy applications

need to possess a novel architecture design for image filtering

and processing. This paper presents a multifunction image

processing system that is accessible over the internet and is

prototyped using a System on Chip (SoC) and FPGA interface. A

pipelined based approach, inspired by a shift register based

Random Access Memory design has been implemented for on-the-fly

computation and minimal use of on-chip resources. The realization

of the system was done using a low cost Spartan 6 FPGA and a

Raspberry-pi B+ representing the ARM cortex based SoC. Data

transfer between the FPGA and SoC has been achieved using a UART

protocol. Computation time of different frame sizes for the system

and standard I.P. software tools have been documented. Chip

utilization and delays have also been reported.

Paper Name: Implementation of MOSFETs in a closed loop H-Bridge

motor driver using charge pumps

Conference Name: India Conference (INDICON), 2015 Annual IEEE

Authors: Ameya Wagh, Nilay Sheth, Jonathon Joshi

Abstract: An efficient modeling of motor drivers using an H Bridge

configuration driven by charge pumps controlled by embedded

components is presented. N-channel MOSFETs and charge pumps

together eliminate the problems of Dead time of MOSFETs and High

values of RDS (ON). The embedded system using an ATMEL

microcontroller drives the load and monitors the load voltages and

input PWM to establish a closed loop system by comparing it with

the stored threshold state space parameters of the motor, also in

turn preventing MOSFET damage by synchronized control over the

gates. Charge pump readings have been reported along with feedback

readings for the microcontroller. Results obtained are in range

with expected outputs.